EuroMIPS Systems

The Microelectronic Expert Team

|

EuroMIPS Systems |

The Microelectronic Expert Team |

| Home Page | Company Profile | Expertise Field | Realizations | Products | EMS Consulting | Resources & Partnership | Job opportunity | EuroMIPS Systems Contact |

| Products |

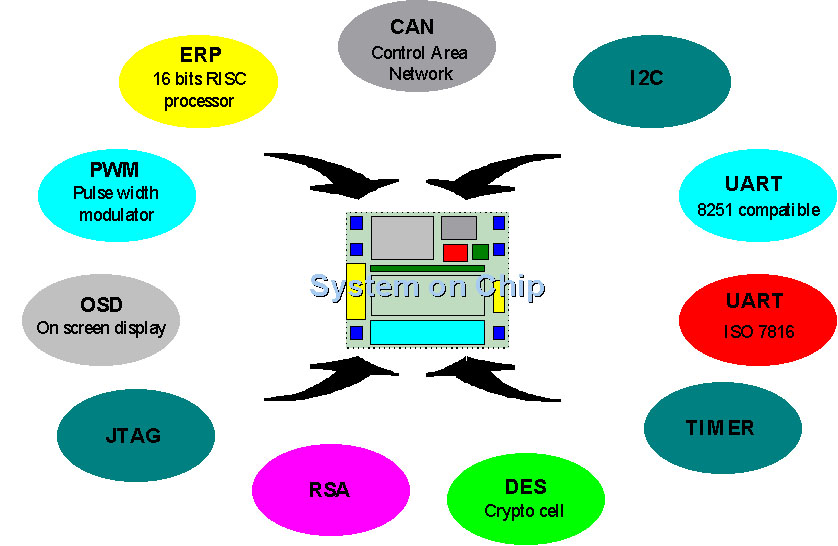

| IP functions |

EuroMIPS Systems developed Intellectual Property (IP) to be reused for system on a chip. Each module is delivered in synthesizable VHDL coming with synthesis script, full set of test benches for verification and validation, with full scan implementation for testability.

|

| CAD Tools development |

Specific tools development to reduce design cycle time, to secure the design and library development and to allow the use of multiple CAD tools.

|

EIEE:

EuroMIPS Systems

Inference

Engine

Explorer

Programmable Electrical and logical Rule Checker |

|

The EuroMIPS Systems Inference Engine Explorer (EIEE) tool provides

designers with an easy way to explore netlist. It allows walking

through the design, identifying patterns, eventually modifiying the

design on fly and writting new designs.

It supports standard cells as well as transistors netlist, accepting as input a spice, LSIM, VHDL or Verilog structural netlist. Outputs are Spice, LSIM, VHDL, Verilog netlist. Application domains are : design rule checking, testability rule checking, electrical rule checking, functional abstraction. |

|

EAC:

EuroMIPS Systems

Automatic

Characterization

Automatic Library Characterization Delay, setup, hold, minimum pulse width, input capacitance extraction |

|

EuroMIPS Systems Automatic Characterization (EAC) tool provides

designers with an efficient and re-usable way to capture patterns

to characterize a cell.

The tool is built around a dedicated language that provides waveform definitions and modifications, automatic delay measurements, support for linear or input slope modeling as well as a bunch of functions for output waveforms checking. This tool is capable of delay, minimum pulse width, setup and hold measurements as well as input pin capacitance calculation. Tool inputs are characterization waveforms and an input spice deck (Eldo, Hspice). Tool outputs are spice out files, and characterization result files. As an example, only one waveform is needed to characterize all NAND gates in a library. |

| (c)copyright EuroMIPS Systems, 2000. | 25/03/00 |